www.ams.com/AS5510

Revision 0.1

8 - 18

AS5510

Datasheet - Detailed Description

The communication from the AS5510 includes:

n Reading the magnetic field strength in 10-bit data

n Reading the status bits

Note: The I?/SPAN>C address of the chip is selected by hardware (pin ADR). Depending on the state of this pin, the I?/SPAN>C address is either

Pin ADR = LOW ? I睠 address = 1010110b(56h)

Pin ADR = HIGH ? I睠 address = 1010111b(57h)

7.2.1 I睠 Interface Data

Note: Operating conditions T

amb

= -30 to +85癈, VDD=2.5 to 3.6V (3V operation) unless otherwise noted.

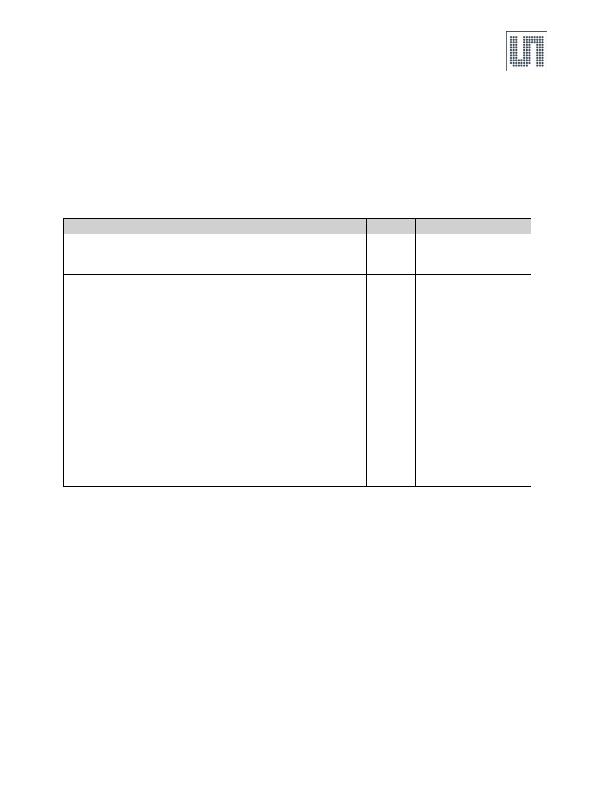

Table 7. I睠 Timings

Symbol

Parameter

Conditions

Min

Typ

Max

Units

f

SCLK

SCL clock frequency

1

MHz

t

BUF

Bus free time; time between STOP and

START condition

0.5

約

t

HD.STA

Hold time; (repeated) START

condition

1

1. After this time the first clock is generated

0.26

約

t

LOW

LOW period of SCL clock

0.5

約

t

HIGH

HIGH period of SCL clock

0.26

約

t

SU.STA

Setup time for a repeated START

condition

0.26

約

t

HD.DAT

Data hold time

2

2. A device must internally provide a hold time of at least 120ns (Fast-mode Plus) for the SDA signal (referred to the V

IHmin

of the SCL) to

bridge the undefined region of the falling edge of SCL.

0.45

約

t

SU.DAT

Data setup time

3

3. A fast-mode device can be used in standard-mode system, but the requirement t

SU.DAT

= 250ns must then be met. This is automatically

the case if the device does not stretch the LOW period of the SCL signal. If such a device does stretch the LOW period of the SCL sig-

nal, it must output the next data bit to the SDA line t

Rmax

+ T

SU.DAT

= 1000 + 250 = 1250ns before the SCL line is released.

50

ns

t

R

Rise time of SDA and SCL signals

120

ns

t

F

Fall time of SDA and SCL signals

4

4. In Fast-mode Plus, fall time is specified the same for both output stage and bus timing. If series resistors are used this has to be consid-

ered for bus timing.

120

ns

t

SU.STO

Setup time for STOP condition

0.26

約

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

ATS137-PL-B-B

IC HALL SENSOR SGL 25MA SIP-3L

ATS177-PG-B-B

IC HALL SENSOR LATCH 25MA SIP-3L

ATS617LSGTN-T

IC HALL EFFECT GEAR SENSOR 4SIP

ATS625LSGTN-T

IC SENSOR GEAR TOOTH 4-SIP

ATS627LSGTN-T

IC HALL EFFECT GEAR SENSOR 4-SIP

ATS635LSETN-T

IC SENSOR GEAR TOOTH 4-SIP

ATS643LSHTN-I2-T

IC SENSOR GEAR TOOTH 4-SIP

ATS645LSHTN-I1

IC SENSOR GEAR TOOTH 4-SIP

相关代理商/技术参数

AS5510-DWLT-1K

功能描述:板机接口霍耳效应/磁性传感器 RoHS:否 制造商:Honeywell 类型:Bipolar Hall-Effect Digital Position Sensor 工作电源电压:3 V to 24 V 电源电流:3.5 mA 最大输出电流:20 mA 工作点最小值/最大值:5 G, 55 G 最小/最大释放点(Brp):- 55 G, - 5 G 最大工作温度:+ 150 C 安装风格:SMD/SMT 封装 / 箱体:SOT-23

AS5510-SO_EK_AB

功能描述:AS5510 - Magnetic, Linear Position Sensor Evaluation Board 制造商:ams 系列:- 零件状态:有效 传感器类型:磁性,线性位置 感应范围:- 接口:I2C 灵敏度:- 电压 - 电源:2.5 V ~ 3.6 V 嵌入式:- 所含物品:板 使用的 IC/零件:AS5510 标准包装:1

AS5510-WL_EK_AB

功能描述:AS5510 - Magnetic, Linear Position Sensor Evaluation Board 制造商:ams 系列:- 零件状态:有效 传感器类型:磁性,线性位置 感应范围:- 接口:I2C 灵敏度:- 电压 - 电源:2.5 V ~ 3.6 V 嵌入式:- 所含物品:板 使用的 IC/零件:AS5510 标准包装:1

AS5510-WL_EK_DB

功能描述:AS5510 - Magnetic, Linear Position Sensor Evaluation Board 制造商:ams 系列:- 零件状态:有效 传感器类型:磁性,线性位置 感应范围:- 接口:I2C 灵敏度:- 电压 - 电源:5V USB 或 9V 嵌入式:是,MCU,8 位 所含物品:板 使用的 IC/零件:AS5510 标准包装:1

AS55110FLF

制造商:TT Electronics / IRC 功能描述:AS55110FLF

AS55110HLF

制造商:TT Electronics / IRC 功能描述:AS55110HLF

AS55110JLF

制造商:TT Electronics / IRC 功能描述:AS55110JLF

AS55111FLF

制造商:TT Electronics / IRC 功能描述:AS55111FLF